成功案例

3D设备堆栈的新会议方法

作者: bet356在线官方网站 点击次数: 发布时间: 2025-07-07 19:28

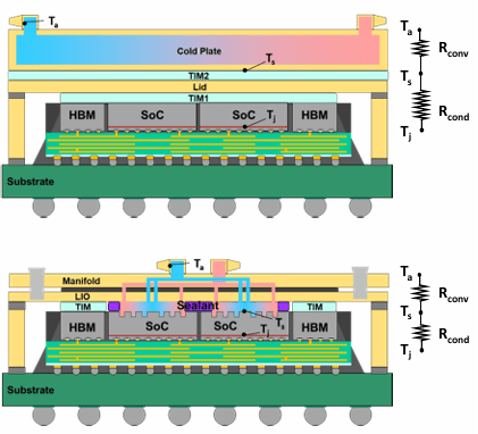

半导体包装的下一个重大跳跃将需要一系列新技术,过程和材料,但是通常,它们将实现数量级以提高性能,这在AI期间很重要。并非所有这些问题都已完全解决,但是最近的电子组件技术会议使我们瞥见了自Chatgpt推出以来,近年来的巨大飞跃对技术界感到震惊。 AMD,TSMC,Samsung,Intel和许多设备供应商详细介绍了混合键合,玻璃核心基板,微通道或直接冷却和通过后电力解决方案进行冷却。高级副总裁兼企业研究员Sam Naffziger在Theai Computing的演讲中对AMD表示:“ AI改变超级计算机/高性能计算领域的方式令人惊讶。” “ Chatgpt和Geminis是互联网数据和受过训练的模型的整个世界,但是高质量的文本数据已完全消耗。AI方法变得更糟E线性智力返回。 TSMC Cowos是直接冷却,包括4个SOC和6 HBM; DRAM和3D多芯片模拟仅在热量和热量的传递中不是产生良好计算系统的一种方式。硅集成微冷器(IMEC-SI)使用有机插入器(COWOS-R)中的1.6倍网式车辆测试了可靠性。散热器设计为模仿4-SOC,8 hbm的包装,并使用40°C的水流速为10 L/min,甚至可能失去3,000瓦的强度。冷却这种液体的方法可与与热接口溶液的间接液体冷却板相关的冷却(最多2.5 w/mm)2功率密度)。图1:用10 l/min水(下)的直接液体冷却牛比TIM,盖子和冷板调节的牛牛会发出更多的热量。资料来源:IEEE ECTC [1] TSMC组装过程应用一个保护层来覆盖SOC后面的铜列。与会议交流载体晶圆并与C4碰撞。翻转和保护性的NA层去除后,在传统的Cowos过程之后,弹性体密封剂分布在SOC周围。密封胶可最大程度地减少翘曲,并密封盖子上的芯片区域。 “在焊接焊接后,一个带有单个入口和出口的歧管将组装成一个集成系统,旨在实现许多冷却室之间的流量分布。”该软件包通过氦气泄漏测试和早期可靠性测试。直接芯片冷却的需求迫切需要佐治亚理工学院提出小说的概念,即chiplets充当冷却剂。 “想象一下,我们设计的芯片是具有不同冷却功能的Ready -to -open社区资源的一部分,例如,直径不同,间距不同,也是不同的TSV设计,” Georgia Tech的3D包装集成中心的总监Muhannad Bakir说。 “我们可以开发独特的TSV结构,这是一个独特的首席运营官LING结构,以及该结构中独特的其他结构,以帮助传输热量和功率。因此,这实际上是仅与堆栈的混合键合解决方案。硅用于芯片-Chip Connections.3)。为放置处理器,内存和基于热的模块的设计灵活性。带有反向功率NetWorkee ECTC的逻辑设备[3] 2nm Gate完全围绕着晶体管应用处理器结构,其后动力网络需要将模块的热量耗散增加20%。三星使用任何元素的边界模型来识别高风险和模仿翘曲的区域。 Mun说:“图形图形设计对于这种包装的异质设计尤为重要,因为薄的RDL容易容易进行热机械应力浓度和裂纹故障。”选择具有更宽的图形宽度和更长图形长度的重新分布层可减少翘曲。成型材料,双面RDL和热界面材料材料ALS已得到进一步改进,以实现更高的导热率和预防热。混合键合的细沥青多层重新分布层(RDL)成为硅内置和层压板底物的可行替代品。 RDL能够以低成本提供高速互连的能力鼓励了这种变化。工业技术研究所(ITRI)和Brewer Science提出了五层聚合物/铜RDL堆栈,其次是铜包装铜混合键合,对于高I/O,高损失损失和高速数字应用中的插入率低。 [4]图4:聚合物/铜堆叠的重新分布层,然后是与受控翘曲的Cu-Cu混合键合。资料来源:IEEE ECTC [4]在玻璃载体晶片中构建线/空间RDL(4至10μML/s)后,使用负碳粉抗和I线的暴露对低K聚合物(2.5)进行了亲子的核对,然后蚀刻,然后是蚀刻,然后在铜上添加钛屏障层,然后平面化A,然后是平面层的含量N铜CMP。将杂化键用热量为300°C(1.06 MPa),然后由紫外线激光执行载体晶圆芯片。聚合物特性(例如低模量,高热稳定性和低吸收性)的设计旨在实现多层RDL堆栈中的低经态。近年来,使用传统电介质(基于SIO2/铜)的杂种键缩放率从10μM(在制造中)扩展到1μm(在研究和开发中)。英特尔高级工程师阿德尔·埃勒比尼(Adel Elherbini)和他的同事讨论了实施此类扩展所需的一些功能。 [5]图5:使用杂种键合的英特尔研究结果。资料来源:IEEE ECTC [5]他们的角色指出,系统体系结构通常确定晶圆到磁力(W2W)或WA是否被选择为沃夫(D2W)键。晶圆到磁力键的主要极限是它必须是相同的芯片键合。这项技术较旧,可提供更明显的间距。晶圆到盘没有尺寸限制粘合,仅使用已知的好晶圆。该集合说:“对于C2W应用程序,而HB间距很重要。” “传统准确性的准确性标准,例如chiplet中心或最坏的信息,不再足够。变形的行为从芯片准备到粘合。-好处。-由于您将电源与信号分开,因此没有一个复杂的方法来加热热量以加热热量,以使热量加热到加热以加热热量,从而加热热量的挑战热量是因为热量峰值和热路模式。互连堆栈中的insity,工作负载和材料属性。 Chidambarrao说:“您取GDS文件,实际上可以将多个级别和层的平均属性一起计算在一起,因此您可以在每个给定位置获得正确的[热传递]平均属性。现在您有一种计算每个瓷砖的方法,您可以对其进行更多完善。”在设计阶段考虑热因子的重要性不能被夸大。他说:“包装和奇普彼此之间正在紧密相互接触,因此这是系统技术的完全问题,您需要担心设计中的热问题。这需要发生。这需要发生,尤其是在背部的背部供应时,我不必这样做,我不必这样做。首席技术人员赫尔曼·奥普林斯(Herman Oprins)说IMEC的热建模和特征R&D团队的负责人。虽然背面的电源最初是一种被动的结构,但它将进一步用于包括信号信号和其他功能。有很多方法可以将其连接起来,但最重要的是,您必须连接正面并通过nanotsv。Nanotsv。Nanotsv。Nanotsv需要至少300nm的薄硅,至少要小于100nm。您的温度较小,因为您的温度较少,因为您的温度较少,因为您的温度却越来越siel(silic)。另一方面,背面有一个金属夹具,因此该密集的金属范围可能会在逻辑逻辑的记忆或记忆中引起10%的热量散射逻辑,而堆栈的记忆对热性能有更大的影响,” Oprins说。“ Loese-Login-Logic or-Logic显示出BSPDN的热效应减少了许多CHIP堆栈。消耗。 [7] Opris强调冷却液体的重要性。 “看3D体系结构,如果您每芯片堆叠5芯片,请说A的100瓦和传统空气冷却的使用,您结束了大于500°C的最高连接温度。每纤维200 GB/s不知道。工程,市场营销和ASE技术促进高级总监Mark Gerber说:“ CPO肯定会发生,这种势头肯定会提前发生。” “在使用CPO时,对热和翘曲的侧面都有敏感性。重要的是,该行业希望保持今天存在的光发动机(即可转换)方面的易插头(即可转换)方面。但是,尽管插头良好的良好性很容易移动,但它们并不容易掌握。在ECTC中,ASE在ASE中显示了其ASIC和ASIC和Etherhet/HBM Sworces Fo的型号平台。R ASIC开关和Etherhet/HBM Co -Apbackage平台。测得的“平面2D波导电路可通过减少完成电缆纤维和手动组装的需求,从而降低下一代CPO解决方案所需的空间,复杂性和成本。在交换过程中进行的步骤是将波导芯埋在玻璃下方,以减少传播的损失。 IEEE ECTC [8]中的曝光银Cowos平台”,IEEE电子组件和技术会议,2025年5月,在出版物中。技术,doi:10.1109/tcpmt.2025.356483.g 1UM音高和AI和计算应用程序的高级载体技术”,IEEE电子组件和技术会议,2025年5月在出版中。

半导体包装的下一个重大跳跃将需要一系列新技术,过程和材料,但是通常,它们将实现数量级以提高性能,这在AI期间很重要。并非所有这些问题都已完全解决,但是最近的电子组件技术会议使我们瞥见了自Chatgpt推出以来,近年来的巨大飞跃对技术界感到震惊。 AMD,TSMC,Samsung,Intel和许多设备供应商详细介绍了混合键合,玻璃核心基板,微通道或直接冷却和通过后电力解决方案进行冷却。高级副总裁兼企业研究员Sam Naffziger在Theai Computing的演讲中对AMD表示:“ AI改变超级计算机/高性能计算领域的方式令人惊讶。” “ Chatgpt和Geminis是互联网数据和受过训练的模型的整个世界,但是高质量的文本数据已完全消耗。AI方法变得更糟E线性智力返回。 TSMC Cowos是直接冷却,包括4个SOC和6 HBM; DRAM和3D多芯片模拟仅在热量和热量的传递中不是产生良好计算系统的一种方式。硅集成微冷器(IMEC-SI)使用有机插入器(COWOS-R)中的1.6倍网式车辆测试了可靠性。散热器设计为模仿4-SOC,8 hbm的包装,并使用40°C的水流速为10 L/min,甚至可能失去3,000瓦的强度。冷却这种液体的方法可与与热接口溶液的间接液体冷却板相关的冷却(最多2.5 w/mm)2功率密度)。图1:用10 l/min水(下)的直接液体冷却牛比TIM,盖子和冷板调节的牛牛会发出更多的热量。资料来源:IEEE ECTC [1] TSMC组装过程应用一个保护层来覆盖SOC后面的铜列。与会议交流载体晶圆并与C4碰撞。翻转和保护性的NA层去除后,在传统的Cowos过程之后,弹性体密封剂分布在SOC周围。密封胶可最大程度地减少翘曲,并密封盖子上的芯片区域。 “在焊接焊接后,一个带有单个入口和出口的歧管将组装成一个集成系统,旨在实现许多冷却室之间的流量分布。”该软件包通过氦气泄漏测试和早期可靠性测试。直接芯片冷却的需求迫切需要佐治亚理工学院提出小说的概念,即chiplets充当冷却剂。 “想象一下,我们设计的芯片是具有不同冷却功能的Ready -to -open社区资源的一部分,例如,直径不同,间距不同,也是不同的TSV设计,” Georgia Tech的3D包装集成中心的总监Muhannad Bakir说。 “我们可以开发独特的TSV结构,这是一个独特的首席运营官LING结构,以及该结构中独特的其他结构,以帮助传输热量和功率。因此,这实际上是仅与堆栈的混合键合解决方案。硅用于芯片-Chip Connections.3)。为放置处理器,内存和基于热的模块的设计灵活性。带有反向功率NetWorkee ECTC的逻辑设备[3] 2nm Gate完全围绕着晶体管应用处理器结构,其后动力网络需要将模块的热量耗散增加20%。三星使用任何元素的边界模型来识别高风险和模仿翘曲的区域。 Mun说:“图形图形设计对于这种包装的异质设计尤为重要,因为薄的RDL容易容易进行热机械应力浓度和裂纹故障。”选择具有更宽的图形宽度和更长图形长度的重新分布层可减少翘曲。成型材料,双面RDL和热界面材料材料ALS已得到进一步改进,以实现更高的导热率和预防热。混合键合的细沥青多层重新分布层(RDL)成为硅内置和层压板底物的可行替代品。 RDL能够以低成本提供高速互连的能力鼓励了这种变化。工业技术研究所(ITRI)和Brewer Science提出了五层聚合物/铜RDL堆栈,其次是铜包装铜混合键合,对于高I/O,高损失损失和高速数字应用中的插入率低。 [4]图4:聚合物/铜堆叠的重新分布层,然后是与受控翘曲的Cu-Cu混合键合。资料来源:IEEE ECTC [4]在玻璃载体晶片中构建线/空间RDL(4至10μML/s)后,使用负碳粉抗和I线的暴露对低K聚合物(2.5)进行了亲子的核对,然后蚀刻,然后是蚀刻,然后在铜上添加钛屏障层,然后平面化A,然后是平面层的含量N铜CMP。将杂化键用热量为300°C(1.06 MPa),然后由紫外线激光执行载体晶圆芯片。聚合物特性(例如低模量,高热稳定性和低吸收性)的设计旨在实现多层RDL堆栈中的低经态。近年来,使用传统电介质(基于SIO2/铜)的杂种键缩放率从10μM(在制造中)扩展到1μm(在研究和开发中)。英特尔高级工程师阿德尔·埃勒比尼(Adel Elherbini)和他的同事讨论了实施此类扩展所需的一些功能。 [5]图5:使用杂种键合的英特尔研究结果。资料来源:IEEE ECTC [5]他们的角色指出,系统体系结构通常确定晶圆到磁力(W2W)或WA是否被选择为沃夫(D2W)键。晶圆到磁力键的主要极限是它必须是相同的芯片键合。这项技术较旧,可提供更明显的间距。晶圆到盘没有尺寸限制粘合,仅使用已知的好晶圆。该集合说:“对于C2W应用程序,而HB间距很重要。” “传统准确性的准确性标准,例如chiplet中心或最坏的信息,不再足够。变形的行为从芯片准备到粘合。-好处。-由于您将电源与信号分开,因此没有一个复杂的方法来加热热量以加热热量,以使热量加热到加热以加热热量,从而加热热量的挑战热量是因为热量峰值和热路模式。互连堆栈中的insity,工作负载和材料属性。 Chidambarrao说:“您取GDS文件,实际上可以将多个级别和层的平均属性一起计算在一起,因此您可以在每个给定位置获得正确的[热传递]平均属性。现在您有一种计算每个瓷砖的方法,您可以对其进行更多完善。”在设计阶段考虑热因子的重要性不能被夸大。他说:“包装和奇普彼此之间正在紧密相互接触,因此这是系统技术的完全问题,您需要担心设计中的热问题。这需要发生。这需要发生,尤其是在背部的背部供应时,我不必这样做,我不必这样做。首席技术人员赫尔曼·奥普林斯(Herman Oprins)说IMEC的热建模和特征R&D团队的负责人。虽然背面的电源最初是一种被动的结构,但它将进一步用于包括信号信号和其他功能。有很多方法可以将其连接起来,但最重要的是,您必须连接正面并通过nanotsv。Nanotsv。Nanotsv。Nanotsv需要至少300nm的薄硅,至少要小于100nm。您的温度较小,因为您的温度较少,因为您的温度较少,因为您的温度却越来越siel(silic)。另一方面,背面有一个金属夹具,因此该密集的金属范围可能会在逻辑逻辑的记忆或记忆中引起10%的热量散射逻辑,而堆栈的记忆对热性能有更大的影响,” Oprins说。“ Loese-Login-Logic or-Logic显示出BSPDN的热效应减少了许多CHIP堆栈。消耗。 [7] Opris强调冷却液体的重要性。 “看3D体系结构,如果您每芯片堆叠5芯片,请说A的100瓦和传统空气冷却的使用,您结束了大于500°C的最高连接温度。每纤维200 GB/s不知道。工程,市场营销和ASE技术促进高级总监Mark Gerber说:“ CPO肯定会发生,这种势头肯定会提前发生。” “在使用CPO时,对热和翘曲的侧面都有敏感性。重要的是,该行业希望保持今天存在的光发动机(即可转换)方面的易插头(即可转换)方面。但是,尽管插头良好的良好性很容易移动,但它们并不容易掌握。在ECTC中,ASE在ASE中显示了其ASIC和ASIC和Etherhet/HBM Sworces Fo的型号平台。R ASIC开关和Etherhet/HBM Co -Apbackage平台。测得的“平面2D波导电路可通过减少完成电缆纤维和手动组装的需求,从而降低下一代CPO解决方案所需的空间,复杂性和成本。在交换过程中进行的步骤是将波导芯埋在玻璃下方,以减少传播的损失。 IEEE ECTC [8]中的曝光银Cowos平台”,IEEE电子组件和技术会议,2025年5月,在出版物中。技术,doi:10.1109/tcpmt.2025.356483.g 1UM音高和AI和计算应用程序的高级载体技术”,IEEE电子组件和技术会议,2025年5月在出版中。 上一篇:国家补贴的第二阶段将于7月继续!官方确认国家 下一篇:前十名应该打超自然的游戏排名

成功案例

正规AG棋牌

QQ:88889999

电话:020-66889888

传真:020-66889777

邮箱:admin@admin.com

地址: 广东省广州市番禺经济开发区58号